Computer Organization, MSIT – 107

Computer Organization, MSIT – 107

Karnataka State Open University

Mukthagangothri, Mysore – 570 006

Second Semester M.Sc in Information Technology

Data Base Management Systems

Preface

An overview of Computer Organization for the Second Semester course in Master Science (IT) curricula.Intoduction to Computer Organization

Unit – 1 COMPUTER ORGANIZATION AND ARCHITECTURE

A computer in its simplest form consists of five components. The control unit controls all activities taking place inside a computer:- accepts information (program and data) through input unit and transfers it to the memory

- information stored in the memory is fetched into an arithmetic and logic unit for processing

- Processed information leaves the computer through an output unit

For e.g., temporary storage of data such as :

- the Instruction Register (IR) This contains the instruction that is currently being executed. Its output is available to the control circuit that generates the timing signals for control of the actual processing circuit needed to execute the instruction.

- the Program Counter (PC) A register contains the memory address of the instruction currently being executed. During the execution of the current instruction, the content of program counter is updated to correspond to the address of the next instruction.

- the Memory Address Register (MAR) This holds the address of the memory location to or from which data is to be transferred.

- Memory Data Register (MDR) This contains the data to be written into or read-out of the addressed of memory location.

- the general-purpose registers These are used for holding data, intermediate results of operations.

- Instruction fetch

- the PC is set to point to the instruction to be executed

- The contents of PC are transferred to the MAR and a Read control signal is sent to the memory

- The content is read out from the addressed memory and loaded into the MDR

- The contents of MDR are transferred to the IR for instruction decoding

- Instruction execution

- The operation field of the instruction in IR is examined to determine the instruction type to be performed by the ALU

- the operand(s) of the instruction are obtained from the memory locations or from GP registers

- The ALU performs the desired operation on one or more operands and sends the result either to memory location or to a GP register. The result is sent to MDR and the address of the location where the result is to be stored is sent to MAR and Write cycle is initiated.

"Computer organization" and "computer architecture" are related terms in the field of computer science, but they refer to different aspects of a computer system.

Here are the key differences between computer organization and computer architecture:

- Computer Organization

- Computer organization refers to the way a computer's hardware components are connected and operate to achieve a specific goal.

- It focuses on the physical components of a computer system, such as the central processing unit (CPU), memory units, input/output (I/O) devices, buses, and control units.

- Computer organization deals with low-level details, including data paths, control signals, timing diagrams, and circuit design.

- It involves the arrangement of various hardware components to ensure that the computer system functions efficiently and effectively.

- Computer organization often influences factors like hardware cost, performance, power consumption, and reliability.

- Computer Architecture

- Computer architecture refers to the design and structure of a computer system, including its instruction set architecture (ISA), memory hierarchy, and system organization.

- It focuses on the high-level attributes of a computer system that affect its performance, functionality, and compatibility.

- Computer architecture defines the ISA, which specifies the set of instructions that a computer can execute and the way these instructions are encoded.

- It encompasses concepts like pipelining, caching, parallel processing, and memory management.

- Computer architecture determines how software interacts with hardware and how various hardware components collaborate to execute programs.

- Changes in computer architecture can have a significant impact on the overall performance and capabilities of a computer system.

A computer's architecture is its abstract model and is the programmer's view in terms of instructions, addressing modes and registers.

Unit – 2 COMPUTER STRUCTURES

A Computer consists of a set of components (CPU, I/O, memory) that communicates with each other via the inter-connection structures.The design of this structure will depend on the type of exchange/transfer that must be made between modules:

- Memory to CPU

- CPU to Memory

- I/O to CPU

- CPU to I/O

- I/O to or from Memory (Direct Memory Access (DMA))

The different functional units of a computer can be connected through a bus structure:

- Single-bus Structure

- Two-bus Structure The I/O transfers are always under the direct control of the processor,

A main memory word can also be used to represent an instruction.

Here,

- the 8 bit operation field can encode 28 (256) distinct instructions

- Addressing information is given in a variety of ways. The different ways in which operands can be named in machine instructions are called addressing modes.

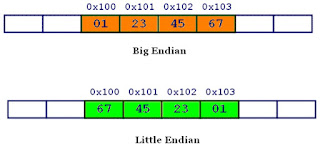

- In little-endian machines, last byte of binary representation of the multibyte data-type is stored first. (last first in address)

- in big-endian machines, first byte of binary representation of the multibyte data-type is stored last.(most first in address)

Unit – 3 MAIN MEMORY OPERATIONS

To execute an instruction, there are two basic operations involving the main memory are needed namely,- Load (or Fetch or Read) The CPU sends the address of the desired location to the main memory and requests to read its contents.

- Store (or Write) The CPU sends the address of the desired location to the main memory, together with the data to be written to that location.

The main memory reads the data stored at that address and sends them to the CPU.

- Three-address instruction format C = A + B is a high level instruction to add the values of the two variables A and B and to assign the sum to a third variable C.

To carry out this instruction, the contents of the memory locations A and B are fetched from the main memory and transferred into the processor – sum is computed – result is sent back to memory and stored in location C.

The same action is performed by a single machine instruction (three address instruction)

Add A,B,C

A processor register called stack pointer(SP) is used to keep track of the address of the element at the top of the stack at any given time.

The processor keeps track of some information about the results of various operations for use by subsequent conditional branch instructions.

This is done by recording the required information into individual bits called as condition code flags.

In some processors, these flags are grouped together in a special register called the condition code register or status register.

Four commonly used flags are:

- N (negative) Sets to 1 if the result is negative; otherwise, cleared to 0

- Z (zero) Sets to 1 if the result is 0; otherwise, cleared to 0

- V (overflow) Sets to 1 if arithmetic overflow occurs; otherwise, cleared to 0

- C (carry) Sets to 1 if carry-out results from the operation; otherwise, cleared to 0

Unit – 4 ADDRESSING MODES AND ASSEMBLY LANGUAGE

The term addressing mode refers to the way used in the operand of an instruction.- Register mode The operand is the contents of a CPU register; the name of register is given in the instruction.

E.g.

Move R1,R2

The contents of R1 is transferred to R2

The address of the memory location is explicitly given in the instruction.

E.g.

Add A,B

The contents of the memory location A is added to the contents of the memory location B. The addresses of A and B are given in the instruction itself.

This mode is used in specifying address and data constants in programs.

E. g.

Move #200, R0

This instruction places the value 200 in register R0.

The register or memory location that contains the address of the operand is called a pointer. We denote indirection by placing the name of the register or the memory address given in the instruction in parenthesis

The register used may be a special register provided for this purpose or may be any one of the general purpose register – referred to as an Index Register.

Module 2 Basic processing Unit

Unit – 5 FUNDAMENTAL CONCEPTS

The processing unit is called central processing unit (CPU).This is also called a processor or instruction set processor (ISP).

It executes machine instructions and coordinates the activities of other units.

To execute a program,

- the CPU fetches one instruction at a time and performs the functions specified.

- Until a branch or a jump instruction is executed, instructions are fetched from successive memory locations.

- The address of the next instruction to be executed is kept by the CPU in a dedicated register called program counter (PC).

- The contents of the PC are updated to point to the next instruction in the sequence.

- Fetch the contents of the memory location by the PC into instruction register (IR)

- Increment the contents of the PC by 1

- Carry out the actions specified by the instruction in the IR.

As instruction execution progresses, data are transferred from one register to another, often passing through the ALU to perform some arithmetic or logic operation.

The instruction decoder and control logic unit is responsible for implementing the actions specified by the instruction loaded in the IR register:

- generates the control signals needed to select the registers involved

- direct the transfer of content on registers

A data transfer in which one device initiates the transfer and waits until the other device responds (with an MFC signal) is referred to as an asynchronous transfer:

1 MAR ← [R1] 2 Request memory READ and put the data to the address register 3 Wait for the Memory Fetch Cycle (MFC) signal and put the result from [MDR] to R2. 4 R2 ←[MDR]Storing a Word in Memory:

1 MAR ← [R1] 2 MDR ←[R2] 3 Request memory WRITE 4 Wait for MFC signalFor each register, two control signals are used:

- to place the contents of that register on the bus, or

- to load the data on the bus into the register.

Suppose that we wish to transfer the contents of register R1 to register R4:

- Enable the output of register R1 This places the contents of R1 on the processor bus.

- Enable the input of register R4 This loads data from the processor bus into register R4.

It performs arithmetic and logic operations on the two operands applied to its‘ A and B inputs.

Unit – 6 PERFORMANCE CONSIDERATIONS

Three of the most important factors in computer's performance are :- the power of the instruction A powerful instruction performs a complex multistep task, at the cost of several clock cycles for execution.

- the clock cycle time, and

- the number of clock cycle per instruction.

Unit – 7 HARD-WIRED CONTROL

Unit – 8 MICROPROGRAMMED CONTROL

Mdule 3 Input-Output Organization

Unit – 9 INTRODUCTION TO INPUT/OUTPUT DEVICES

A simple arrangement to connect I/O devices to a computer is to use a single bus arrangement, it consists of three sets of lines used to carry address, data, and control signals.- Each I/O device is assigned a unique set of addresses.

- When the processor places a particular address on the address lines, the device that recognizes this address responds to the commands(read, write) issued on the control lines.

With memory-mapped I/O, any machine instruction that accesses memory can be used to transfer data to or from an I/O device.

留言